#### MICROPROCESSORS (SUBJECT CODE-CE0506/CS0506) UNIT-1 B.TECH (CE/CSE) SEMESTER-V

#### Shikha Singh

Academic Year 2019-2020

#### **Uni Chapters**

t

#### **1** Introduction to 8085 Microprocessor

Basic functions of the microprocessor, System bus, Architecture, Pin Configuration and Programmer's model of Intel 8085 Microprocessor. Overview of the instruction groups of 8085 and the addressing modes..

#### 2 Intel 8086 Architecture:

features of 8086 processor, 8086/88 CPU Architecture and the pipelined operation, Programmer's Model and Segmented Memory.

#### **Designing the 8086 CPU module:**

8086 pin description in details, Generating the 8086 System Clock and Reset Signals, 8086 Minimum and Maximum Mode CPU Modules, Minimum and Maximum Mode Timing Diagrams, Interrupt Structure, Interrupt Processing and the Predefined interrupts in

4

#### 3 Instruction Set of 8086 and Programming:

Instruction Set of 8086 microprocessor in details, Addressing modes of 8086/88, Programming the 8086 in assembly language, Mixed mode programming with C-language and assembly.

#### Peripheral Controllers for 8086 family and System Design:

Functional Block Diagram and description, Control Word Formats, Operating Modes and Applications of the Peripheral Controller namely 8255-PPI, 8253-PIT, 8259- PIC and 8237-DMAC. Interfacing of the above Peripheral Controllers. Keyword and Display Interface using 8255. Memory Interfacing: SRAM, ROM and DRAM (using a typical DRAM Controller such as Intel 8203). System Design based on the Memory and Peripherals

#### Multiprocessor Systems:

Study of Multiprocessor Configurations namely Tightly Coupled System (TCS) and Loosely Coupled System (LCS), TCS with the case study of the Coprocessor, Various System Bus Arbitration Schemes in LCS, and Role of the Bus Arbiter (Intel 8289) in the LCS.

#### Books Text Book:

1) Microprocessor architecture and applications with 8085: By Ramesh Gaonkar (Penram

International Publication).

2) 8086/8088 family: Design Programming and Interfacing: By John Uffenbeck (Pearson

Education).

3) 8086 Microprocessor Programming and Interfacing the PC: By Kenneth Ayala

4) Microcomputer Systems: 8086/8088 family Architecture, Programming and Design: By

Liu & Gibson (PHI Publication).

5) Microprocessor and Interfacing: By Douglas Hall (TMH Publication).

#### Ref. Books:

- 1) Advanced Microprocessor: By Roy & Bhurchandi (Tata McGraw Hill).

- 2) Advanced Microprocessors: By Daniel Tabak (McGraw Hill)

- 3) The SPARC Architecture Manual (Version 8).

- 4) Intel Manuals.

### Introduction to 8085 Microprocessor

Basic functions of the microprocessor, System bus, Architecture, Pin Configuration and Programmer's model of Intel 8085 Microprocessor. Overview of the instruction groups of 8085 and the addressing modes. (No programming based on 8085).

# Definition of the Microprocessor

- The microprocessor is a

- Multipurpose,

- Programmable,

- <u>Clock-driven</u>,

- Register-based Electronic device that reads binary instructions from the storage device called memory and takes in binary data and process it according to those instructions and provides result as output.

### **Programmable Machine**

#### **Programmable Machine**

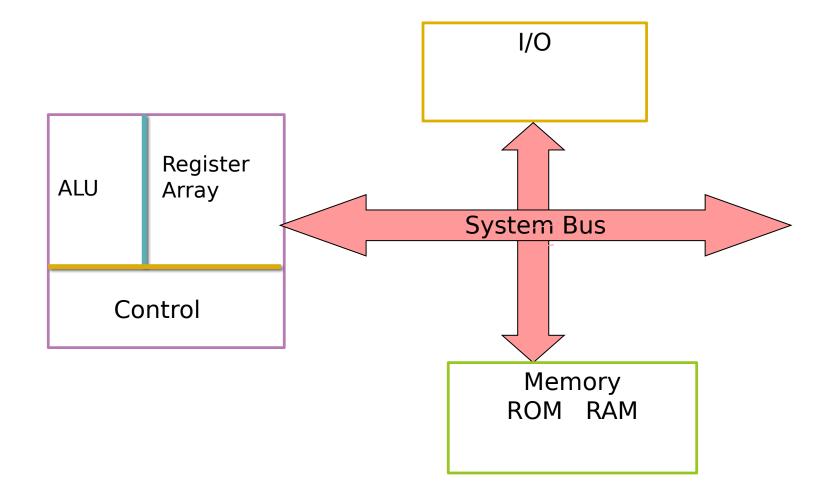

- Internally, the microprocessor is made up of 3 main units.

- The Arithmetic/Logic Unit (ALU)

- The Control Unit.

- An array of registers for holding data while it is being manipulated.

#### Arithmetic/Logic Unit

• Performs all computing and logic operations such as addition and subtraction as well as AND, OR and XOR.

#### Register Array

A collection of registers within the microprocessor itself. These are used primarily for data storage during program execution. The number and the size of these registers differ from one microprocessor to the other

#### Control Unit

As the name implies, the control Unit controls what is happening in the microprocessor. It provides the necessary control and timing signals to all operations in the microprocessor as well as it contact to the outside world.

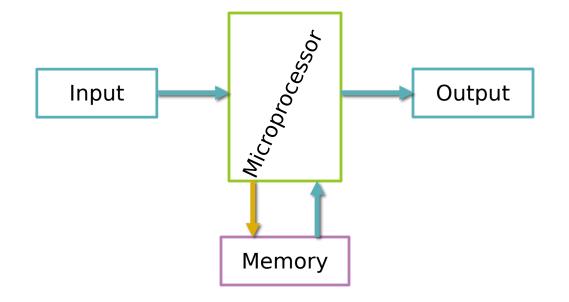

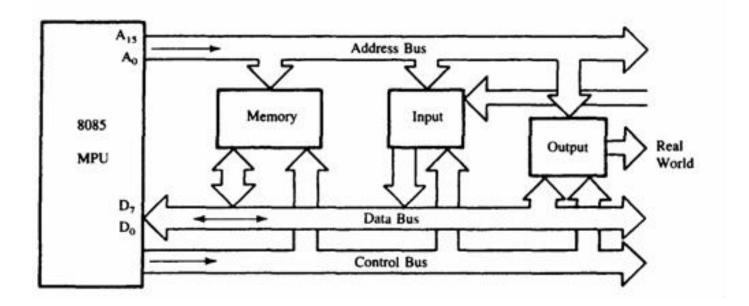

### Organization of a microprocessorbased system

### Memory

Memory stores information such as instructions and data in binary format (0 and 1). It provides this information to the microprocessor whenever it is needed.

# Memory(1)

#### Read Only Memory (ROM) (Non - Volatile)

used to store information that does not change.

- Random Access Memory (RAM) (also known as Read/Write Memory).

- used to store information supplied by the user. Such as data.

# I/O (Input/Output)- peripherals.

- Input devices : transfer <u>binary</u> information from the outside world to the microprocessor.

- Examples of input devices are: keyboard, mouse, bar code reader, scanner etc.

- **Output devices**: transfer <u>binary</u> information from the microprocessor to the outside world.

- Theses include things like an LED, a monitor, a printer etc.

# System Bus

- It is simply a group of wires carrying the voltages and curents representing the different bit values.

- The microprocessor communicates with only one peripheral at a time and the Controlling the bus is done by the Control Unit.

### Program

- Program: A program is a sequence of instructions that bring data into the microprocessor, processes it and sends it out.

- There are many programming languages (C, C++, FORTRAN etc.) However, these programming languages can be grouped into three main levels

# Continue...

Programming Languages

#### Machine language

Machine language is the lowest level programming language. It is a language intended to be understood by the microprocessor (the machine) only. In this language, every instruction is described by binary patterns.

```

e.g. 11001101 may mean 1 + 3

```

This is the form in which instructions are stored in memory. This is the only form that the microprocessor understands.

## Continue....

> Programming Languages

#### Assembly language

- This language is more understandable by humans. In this language, the binary patterns are assigned mnemonics (short abbreviated names).

- There is usually one assembly language instruction for each machine language instruction.

e.g. "Add 1,3" is assigned to the machine language pattern 11001101 mentioned above to refer to the operation 1+3.

# Continue....

> Programming Languages

#### High level languages

- These are languages like C, PASCAL and Java. These are more natural for humans to use than assembly or machine languages. They are also more compact.

- One high level instruction translates into many assembly or machine language instructions.

e.g. z = y + x may translate into:

MOV R1,#20H MOV R2,#30H ADD R1,R2

# The three cycle instruction execution model

- To execute a program, the microprocessor "reads" each instruction from memory, "interprets" it, then "executes" it.

- > To use the right names for the cycles:

The microprocessor **fetch** each instruction, **<u>decodes</u>** it,

#### Then <u>execute</u> it.

This sequence is continued until all instructions are performed.

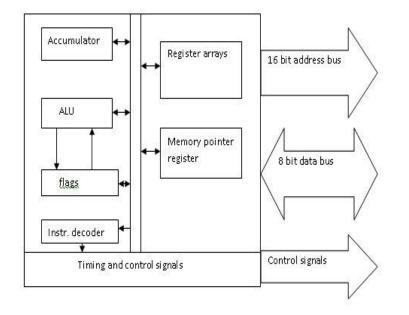

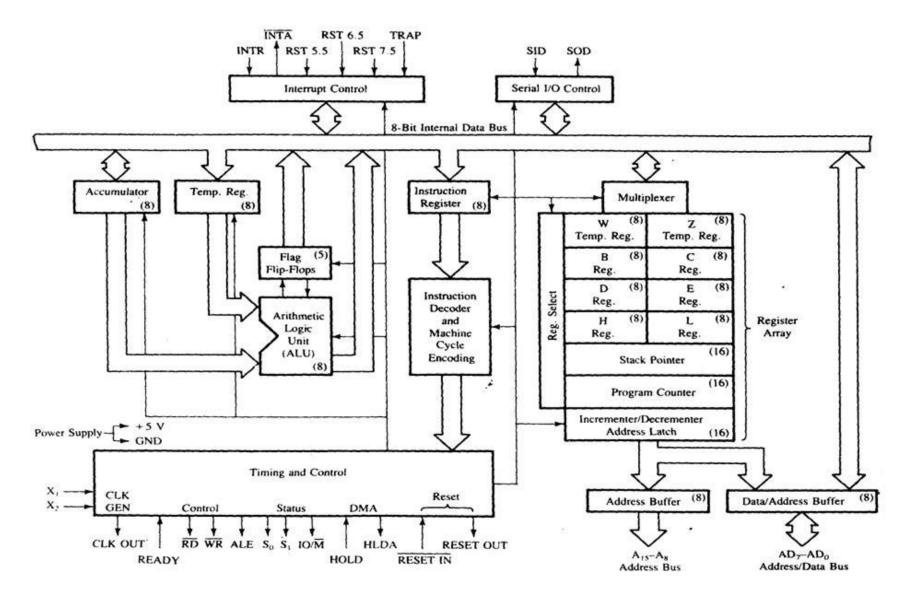

### 8085 Microprocessor Architecture

# The 8085 Hardware Model & Programming Model

Accumulator A flag register в С D Е н L Stack pointer SP PC. Data bus Address bus 16 00 lines lines Bidirectional unidirectional

Fig. 1 8085 Hardware Model

Fig.2 8085 Programming Model

### 8085 Microprocessor Architecture

### 8085 Hardware Model

- Fig 1 Shows the hardware model of 8085. it contains two major segment. One segment includes arithmetic / logic unit (ALU), accumulator, flag register and instruction decoder.

- The second segment shows various 8-bit and 16bit registers.

- The 8085 uses 8-bit bidirectional data bus, 16bit unidirectional address bus and control bus.

# 8085 Programming Model

- The programming model represents the various registers of the microprocessor. It is very useful to write assembly language programs.

- The 8085 Programming model includes six registers, one accumulator and one flag register and it has two 16 bit registers **Stack Pointer(SP)** and **Program Counter (PC)** shown in figure 2.

# 8085 Programming Model (2)

#### Registers

The 8085 has 6 general purpose registers to store 8-bit data. These are identifies as a B,C,D,E,H,L.

They can be combines as register pairs BC,DE,HL to perform 16-bit operations

#### Accumulator

The accumulator is a 8-bit register that is part of ALU. This register is used to store the 8 bit data and to perform the arithmetic and logical operations. The result of operation is stored in to accumulator.

# 8085 Programming Model (3)

### \_ Flags

The ALU includes five flip-flops , which are set or reset after an operation according to data conditions of the result in accumulator and other registers. The y are called Zero (Z) , Carry (Cy) , Sign (S) , Parity (P) , Auxiliary Carry (AC) flags.  $D_7$   $D_6$   $D_5$   $D_4$   $D_3$   $D_2$   $D_1$   $D_0$

|   |     |    | ~    | -    |        | U      |

|---|-----|----|------|------|--------|--------|

| Z | < 1 | AC |      | P    |        | CY     |

|   | Z   | Z  | Z AC | Z AC | Z AC P | Z AC P |

8085 Flag Register

# Flag Register

- Zero Flag (Z): The zero flag is set when the result is zero, otherwise it is reset.

- Carry Flag (CY): If an arithmetic operation results in carry, the carry flag is set, otherwise it is reset.

- Sign Flag(S): Sign flag is set if the D7 of the result is 1, otherwise it is reset.

- Parity Flag(P): If the result has an even number of 1's the flag is set, for an odd number of 1's it is reset.

- Auxiliary Carry (AC): In an arithmetic operation, when a carry is generated by digit D3 and passed to D4, the AC flag is set. Used for BCD operations.

### Program Counter (PC) & Stack Pointer(SP)

\_ These are the two 16-bit registers to hold the memory address.

**PC**:

Microprocessor use the PC to Sequence the Execution of the Program.

Function of the program counter is to point the memory address from which next byte is to be fetched.

PC contains the Address of the next instruction to be Executed SP:

The SP points to the R/W memory location and **it is used for the temporary** storage of the Data.

### 8085 Instruction Classification

\_ The 8085 instructions can be classified as the following five categories:

| <ul> <li>Data transfer Operations</li> <li>Between registers</li> <li>Specific data byte to a<br/>Register from memory<br/>location</li> <li>Between a Memory location<br/>and Register</li> <li>Between I/O device and the<br/>Accumulator</li> </ul> | <ul> <li>Arithmetic Operations</li> <li>Addition</li> <li>Subtraction</li> <li>Increment / Decrement</li> </ul>                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Logical Operations</li> <li>AND , OR , X-OR ,</li> <li>Rotate , Compare ,</li> <li>Complement</li> </ul>                                                                                                                                      | <ul> <li>Branching Operations</li> <li>Jump : Conditional &amp;</li> <li>Unconditional</li> <li>Call , Return and Restart</li> </ul> |

| <ul> <li>Machine Control Operations</li> <li>Halt , Interrupt or Do nothing</li> </ul>                                                                                                                                                                 |                                                                                                                                      |

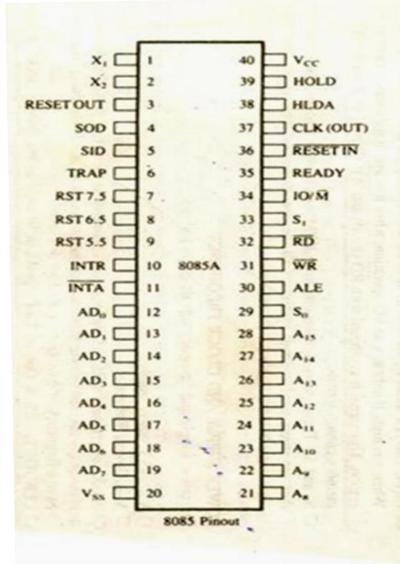

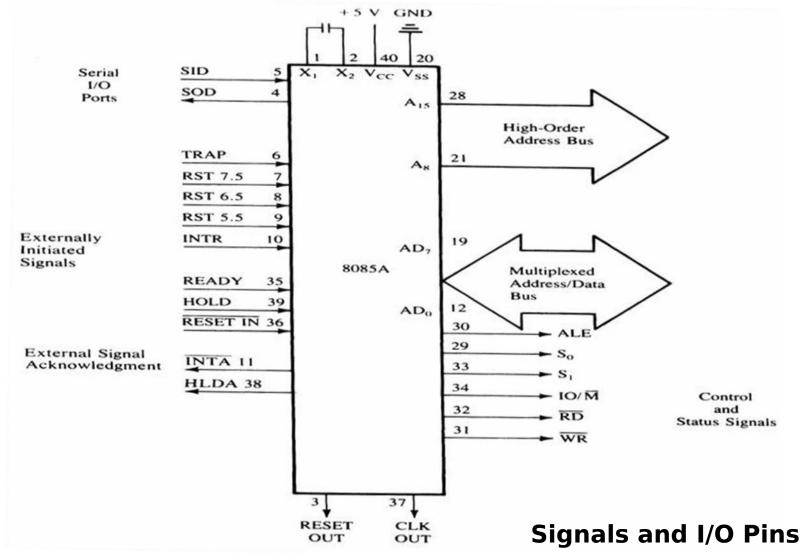

### Intel 8085 Pin Configuration

# Signals

# **Clock Pins**

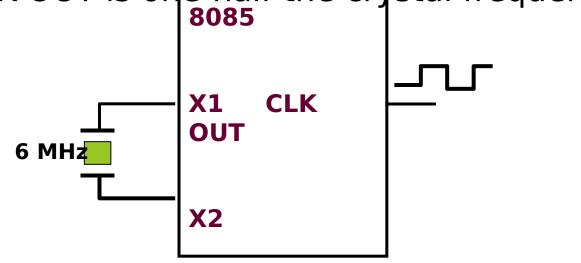

8085 MPU has 3 pins that control or present the clock signal.

- X1 and X2 pins determine the clock frequency.

- CLK OUT is a square-wave output clock.

• The CLOCK OUT is one-half the crystal frequency.

### 8085 Pinout

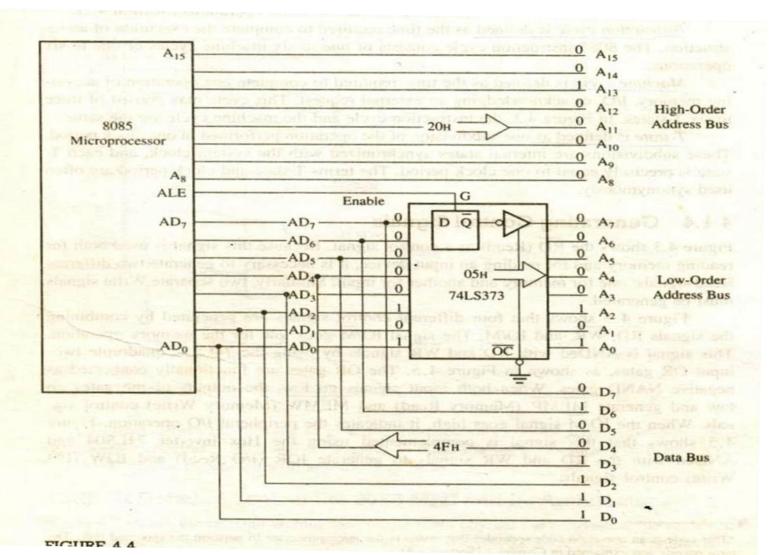

- 8085 μp consists of 16 signal pins use as address bus.

- Divide into 2 part: A15 A8 (upper) and AD7 – AD0 (lower).

- A15 A8 : Unidirectional, known as 'high order address bus'.

- AD7 AD0 : bidirectional and dual purpose (address and data placed once at a time).

- AD7 AD0 also known as 'low order address'.

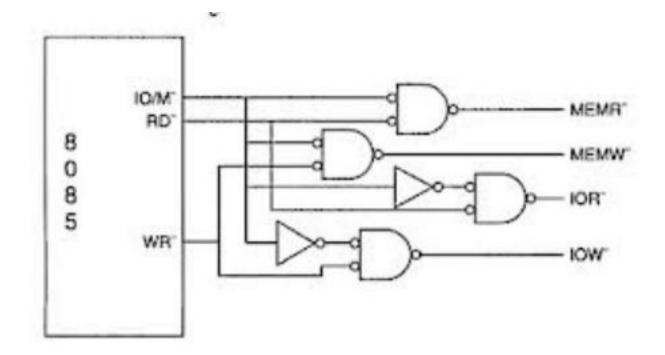

# Control and Status Signals

### • Signals:

- RD Read (active low). To indicate that the I/O or memory selected is to be read and data are available on the bus.

- WR Write: Active low. This is to indicate that the data available on the bus are to be written to memory or I/O ports.

- IO/M To differentiate I/O operation or memory operations.

- '0' indicates a memory operation.

- 'T'-indicates an I/O operation.

- IO/M combined with RD and WR to generate I/O and memory control signals.

- S1 and S0: Status signals, similar to IO/M, can identify various operations as shown on the following table :

#### TABLE 4.1

8085 Machine Cycle Status and Control Signals

|                       | Status |                |     |                                                                                               |  |

|-----------------------|--------|----------------|-----|-----------------------------------------------------------------------------------------------|--|

| Machine Cycle         | IO/M   | S <sub>1</sub> | So  | <b>Control Signals</b>                                                                        |  |

| Opcode Fetch          | 0      | 1              | 1   | $\overline{\text{RD}} = 0$                                                                    |  |

| Memory Read           | 0      | 1              | 0   | $\overline{RD} = 0$                                                                           |  |

| Memory Write          | 0      | 0              | 1   | $\overline{WR} = 0$                                                                           |  |

| I/O Read              | 1      | 1              | 0   | $\overline{RD} = 0$                                                                           |  |

| I/O Write             | 1      | 0              | 1   | $\overline{WR} = 0$                                                                           |  |

| Interrupt Acknowledge | 1      | 1              | 1   | $\overline{INTA} = 0$                                                                         |  |

| Halt                  | Z      | 0              | 0 ] |                                                                                               |  |

| Hold                  | Z      | Х              | x   | $\overline{\text{RD}}, \overline{\text{WR}} = \text{Z} \text{ and } \overline{\text{INTA}} =$ |  |

| Reset                 | Z      | Х              | x   |                                                                                               |  |

NOTE: Z = Tri-state (high impedance)

X = Unspecified

| <b>S1</b> | <b>S</b> 0 | Statu<br>s |

|-----------|------------|------------|

| 0         | 0          | Halt       |

| 0         | 1          | Write      |

| 1         | 0          | Read       |

| 1         | 1          | Fetch      |

#### 8085 Bus Structure

# Interrupt Signals

# $\bullet 8085~\mu p$ has several interrupt and external intiated signals as shown in the following table.

#### TABLE 4.2

8085 Interrupts and Externally Initiated Signals

| INTR (Input)                           | Interrupt Request: This is used as a general-purpose interrupt; it is simi-<br>lar to the INT signal of the 8080A.                                                                                                                                                 |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTA (Output)                          | Interrupt Acknowledge: This is used to acknowledge an interrupt.                                                                                                                                                                                                   |

| RST 7.5 (Inputs)<br>RST 6.5<br>RST 5.5 | Restart Interrupts: These are vectored interrupts that transfer the pro-<br>gram control to specific memory locations. They have higher priorities<br>than the INTR interrupt. Among these three, the priority order is 7.5,<br>6.5, and 5.5.                      |

| TRAP (Input)                           | This is a nonmaskable interrupt and has the highest priority.                                                                                                                                                                                                      |

| HOLD (Input)                           | This signal indicates that a peripheral such as a DMA (Direct Memory Access) controller is requesting the use of the address and data buses.                                                                                                                       |

| HLDA (Output)                          | Hold Acknowledge: This signal acknowledges the HOLD request.                                                                                                                                                                                                       |

| READY (Input)                          | This signal is used to delay the microprocessor Read or Write cycles un-<br>til a slow-responding peripheral is ready to send or accept data. When<br>this signal goes low, the microprocessor waits for an integral number<br>of clock cycles until it goes high. |

# Interrupt signals

- An interrupt is a hardware-initiated subroutine CALL.

- When interrupt pin is activated, an ISR will be

| <u>called</u> , interrupting the pro- | cogram that is currently |   |

|---------------------------------------|--------------------------|---|

|                                       |                          | _ |

| Pin            | Subroutine Location |

|----------------|---------------------|

| TRAP           | 0024 <b>H</b>       |

| <b>RST</b> 5.5 | 002 <b>CH</b>       |

| <b>RST</b> 6.5 | 0034 <b>H</b>       |

| <b>RST</b> 7.5 | 003 <b>CH</b>       |

# RESET signal

- Following are the two kind of RESET signals:

- RESET IN: an active low input signal, Program Counter (PC) will be set to 0 and thus MPU will reset.

- RESET OUT: an output reset signal to indicate that the μp was reset (i.e. RESET IN=0). It also used to reset external devices.

# ALE signal

• ALE means Address latch Enable and it is used to Demultiplex the lower order address and data lines.

# ALE used to Demultiplex address/data bus

#### Generation of Control signal

# SID and SOD signal

# •SID:-

SID is serial input data pin. The bit data on this line is loaded in the seventh bit of the accumulator whenever a RIM instruction is executed.

# •SOD:-

SOD is serial output data. The output SOD is set or reset as specified by the SIM instruction

# Instruction

- An instruction is a command to the Microprocessor to perform a given task on Specific data.

- Each instruction has 2- parts

- Op-Code

- Operands

#### Instruction Word Size:

- Instruction are commonly referred to in terms of Byte

- 1 Byte Instruction (Ex. MOV E,A , ADD E , CMA )

- 2 Byte Instruction (Ex. MVI A, 35H, MVI B,29H)

- \_ 3 Byte Instruction (Ex. LDA 2055H, JMP 2080H)

#### **Instruction Set of 8085**

An instruction is a binary pattern designed inside a microprocessor to perform a specific function.

•The entire group of instructions that a microprocessor supports is called *Instruction Set*.

o 8085 has 246 instructions.

Each instruction is represented by an 8-bit binary value.

These 8-bits of binary value is called *Op-Code* or *Instruction Byte*.

## **Classification of Instruction Set**

o Data Transfer Instruction

oArithmetic Instructions

oLogical Instructions

oBranching Instructions

• Machine Control Instructions

These instructions move data between registers, or between memory and registers.

These instructions copy data from source to destination.

While copying, the content of source is not modified.

| Opcode | Operand                 | Description                      |

|--------|-------------------------|----------------------------------|

| MOV    | Rd,Rs<br>M, Rs<br>Rd, M | Copy from source to destination. |

This instruction copies the contents of the source register into the destination register.

• The contents of the source register are not altered.

If one of the operands is a memory location, its location is specified by the contents of the HL registers.

• **Example**: MOV D,E or MOV B, A

| Opcode | Operand             | Description          |

|--------|---------------------|----------------------|

| MVI    | Rd, Data<br>M, Data | Move immediate 8-bit |

•The 8-bit data is stored in the destination register or memory.

If the operand is a memory location, its location is specified by the contents of the H-L registers.

• Example: MVI B, 75H or MVI M, 55H

| Opcode | Operand        | Description             |

|--------|----------------|-------------------------|

| LDA    | 16-bit address | Load Accumulator Direct |

The contents of a memory location, specified by a 16-bit address in the operand, are copied to the accumulator.

• The contents of the source are not altered.

o Example: LDA 2037H

| Opcode | Operand              | Description               |

|--------|----------------------|---------------------------|

| LDAX   | B/D Register<br>Pair | Load accumulator indirect |

- o The contents of the designated register pair point to a memory location.

- o This instruction copies the contents of that memory location into the accumulator.

- o The contents of either the register pair or the memory location are not altered.

- o Example: LDAX D

| Opcode | Operand                    | Description                  |

|--------|----------------------------|------------------------------|

| LXI    | Reg. pair, 16-<br>bit data | Load register pair immediate |

oThis instruction loads 16-bit data in the register pair.

o **Example**: LXI H, 2074 H

o This instruction store 74H in L and 20H in H.

| Opcode | Operand        | Description               |

|--------|----------------|---------------------------|

| LHLD   | 16-bit address | Load H-L registers direct |

- o This instruction copies the contents of memory location pointed out by 16-bit address into register L.

- o It copies the contents of next memory location into register H.

- o Example: LHLD 2050H

- o Location 2050H contains 20H and 2051H contains 21H

- o 21H will be loaded in to H and 20H will be loaded in to L

| Opcode | Operand        | Description              |

|--------|----------------|--------------------------|

| STA    | 16-bit address | Store accumulator direct |

oThe contents of accumulator is copied into the memory location specified by the operand.

oExample: STA 2050 H

| Opcode | Operand       | Description                |

|--------|---------------|----------------------------|

| STAX   | B/D Reg. pair | Store accumulator indirect |

oThe contents of accumulator are copied into the memory location specified by the contents of the register pair.

o **Example**: STAX B

| Opcode | Operand        | Description                |

|--------|----------------|----------------------------|

| SHLD   | 16-bit address | Store H-L registers direct |

oThe contents of register L are stored into memory location specified by the 16-bit address.

oThe contents of register H are stored into the next memory location.

Conten

Content

t of L

250

250

oExample: SHLD 2500 H

| Opcode | Operand | Description           |

|--------|---------|-----------------------|

| XCHG   | None    | Exchange H-L with D-E |

oThe contents of register H are exchanged with the contents of register D.

oThe contents of register L are exchanged with the contents of register E.

oExample: XCHG

| Opcode | Operand | Description                             |

|--------|---------|-----------------------------------------|

| SPHL   | None    | Copy H-L pair to the Stack Pointer (SP) |

oThis instruction loads the contents of H-L pair into SP.

#### o**Example**: SPHL

oH provides the higher order byte and L provides the lower order byte.

| Opcode | Operand | Description                    |

|--------|---------|--------------------------------|

| XTHL   | None    | Exchange H-L with top of stack |

oThe contents of L register are exchanged with the location pointed out by the contents of the SP.

oThe contents of H register are exchanged with the next location (SP + 1).

o Example: XTHL

| Opcode | Operand | Description                            |

|--------|---------|----------------------------------------|

| PCHL   | None    | Load program counter with H-L contents |

- oThe contents of registers H and L are copied into the program counter (PC).

- oThe contents of H are placed as the high-order byte and the contents of L as the low-order byte.

o**Example**: PCHL

| Opcode | Operand   | Description                   |

|--------|-----------|-------------------------------|

| PUSH   | Reg. pair | Push register pair onto stack |

oThe contents of register pair are copied onto stack.

oSP is decremented and the contents of high-order registers (B, D, H, A) are copied into stack.

oSP is again decremented and the contents of loworder registers (C, E, L, Flags) are copied into stack.

o**Example**: PUSH B

| Opcode | Operand   | Description                       |

|--------|-----------|-----------------------------------|

| POP    | Reg. pair | Pop of the stack to register pair |

oThe contents of top of stack are copied into register pair.

oThe contents of location pointed out by SP are copied to the low-order register (C, E, L, Flags).

oSP is incremented and the contents of location are copied to the high-order register (B, D, H, A).

o**Example**: POP H

LXI H,2525h MVI M,25h MOV B,M MVI L,26h MVI M,26H MOV C,M SHLD 4000h LDAX B SPHL

| Opcode | Operand   | Description                           |

|--------|-----------|---------------------------------------|

| ADD    | R or<br>M | Add register or memory to accumulator |

oThe contents of register or memory are added to the contents of accumulator.

oThe result is stored in accumulator.

olf the operand is memory location, its address is specified by H-L pair.

oAll f lags are modified to reflect the result of the addition.

#### oExample: ADD C or ADD M

| Opcode | Operand | Description                           |

|--------|---------|---------------------------------------|

| ADC    | R or    | Add register or memory to accumulator |

|        | Μ       | with carry                            |

oThe contents of register or memory and Carry Flag (CY) are added to the contents of accumulator.

oThe result is stored in accumulator.

o If the operand is memory location, its address is specified by H-L pair.

oAll f lags are modified to reflect the result of the addition.

oExample: ADC D or ADC M

| Opcode | Operand    | Description                  |

|--------|------------|------------------------------|

| ADI    | 8-bit data | Add immediate to accumulator |

oThe 8-bit data is added to the contents of accumulator.

o The result is stored in accumulator.

oAll f lags are modified to reflect the result of the addition.

o Example: ADI 49 H

| Opcode | Operand    | Description                             |

|--------|------------|-----------------------------------------|

| ACI    | 8-bit data | Add immediate to accumulator with carry |

oThe 8-bit data and the Carry Flag (CY) are added to the contents of accumulator.

oThe result is stored in accumulator.

oAll f lags are modified to reflect the result of the addition.

#### o Example: ACI 48 H

| Opcode | Operand   | Description                   |

|--------|-----------|-------------------------------|

| DAD    | Reg. pair | Add register pair to H-L pair |

oThe 16-bit contents of the register pair are added to the contents of H-L pair.

oThe result is stored in H-L pair.

olf the result is larger than 16 bits, then CY is set.

oNo other f lags are changed.

#### oExample: DAD D

| Opcode | Operand | Descriptio                       |

|--------|---------|----------------------------------|

| Opcode | Operand | n                                |

| SUB    | R or    | Subtract register or memory from |

| 500    | M       | accumulator                      |

oThe contents of the register or memory location are subtracted from the contents of the accumulator.

o The result is stored in accumulator.

olf the operand is memory location, its address is specified by H-L pair.

oAll f lags are modified to reflect the result of subtraction.

o **Example:** SUB H or SUB M

| Opcode | Operand      | Description                                              |

|--------|--------------|----------------------------------------------------------|

| SBB    | R<br>or<br>M | Subtract register or memory from accumulator with borrow |

oThe contents of the register or memory location and Borrow Flag (i.e. CY) are subtracted from the contents of the accumulator.

olf the operand is memory location, its address is specified by H-L pair.

oAll flags are modified to reflect the result of subtraction.

o **Example**: SBB D or SBB M

| Opcode | Operand    | Description                         |

|--------|------------|-------------------------------------|

| SUI    | 8-bit data | Subtract immediate from accumulator |

oThe 8-bit data is subtracted from the contents of the accumulator.

o The result is stored in accumulator.

o All f lags are modified to reflect the result of subtraction.

o Example: SUI 55 H

| Opcode | Operand    | Description                                        |

|--------|------------|----------------------------------------------------|

| SBI    | 8-bit data | Subtract immediate from<br>accumulator with borrow |

oThe  $\,8\text{-bit}$  data and the Borrow Flag (i.e. CY) is subtracted from the contents of the accumulator.

oThe result is stored in accumulator.

oAll f lags are modified to reflect the result of subtraction.

o Example: SBI 65 H

| Opcode | Operand      | Description                       |

|--------|--------------|-----------------------------------|

| INR    | R<br>or<br>M | Increment register or memory by 1 |

oThe contents of register or memory location are incremented by 1.

oThe result is stored in the same place.

olf the operand is a memory location, its address is specified by the contents of H-L pair.

o **Example**: INR D or INR M

| Opcode | Operand | Description                  |

|--------|---------|------------------------------|

| INX    | R       | Increment register pair by 1 |

oThe contents of register pair (B, D, H, SP)are incremented by 1.

oThe result is stored in the same place.

oNo flags are affected.

oExample: INX B

| Opcode | Operand      | Description                       |

|--------|--------------|-----------------------------------|

| DCR    | R<br>or<br>M | Decrement register or memory by 1 |

oThe contents of register or memory location are decremented by 1.

oThe result is stored in the same place.

olf the operand is a memory location, its address is specified by the contents of H-L pair.

o **Example**: DCR C or DCR M

| Opcode | Operand | Descriptio                   |

|--------|---------|------------------------------|

|        |         | n                            |

| DCX    | R       | Decrement register pair by 1 |

oThe contents of register pair(B,D,H,SP) are decremented by 1.

oThe result is stored in the same place.

oNo flags are affected.

#### oExample: DCX D

| Opcode | Operand      | Description                                    |

|--------|--------------|------------------------------------------------|

| СМР    | R<br>or<br>M | Compare register or memory<br>with accumulator |

oThe contents of the operand (register or memory) are compared with the contents of the accumulator.

oBoth contents are preserved .

oThe result of the comparison is shown by setting the flags of the PSW as follows:

- •if (A) < (reg/mem): carry flag is set

- if (A) = (reg/mem): zero flag is set

- if (A) I (reg/mem): carry and zero flags are reset.

- Example: CMP C or CMP M

| Opcode | Operand    | Description                        |

|--------|------------|------------------------------------|

| СЫ     | 8-bit data | Compare immediate with accumulator |

oThe 8-bit data is compared with the contents of accumulator.

oThe values being compared remain unchanged.

oThe result of the comparison is shown by setting the flags of the PSW as follows:

- \_ if (A) < data: carry f lag is set

- \_ if (A) = data: zero f lag is set

- \_ if (A)  $\mid$  data: carry and zero f lags are

reset

#### Example: CPI 87H

| Opcode | Operand      | Description                                     |

|--------|--------------|-------------------------------------------------|

| ANA    | R<br>or<br>M | Logical AND register or memory with accumulator |

oThe contents of the accumulator are logically ANDed with the contents of register or memory.

oThe result is placed in the accumulator.

oS, Z, P are modified to reflect the result of the operation.

o**Example**: ANA C or ANA M.

| Opcode | Operand    | Description                            |

|--------|------------|----------------------------------------|

| ANI    | 8-bit data | Logical AND immediate with accumulator |

oThe contents of the accumulator are logically ANDed with the 8-bit data.

oThe result is placed in the accumulator.

oS, Z, P are modified to reflect the result.

o**Example**: ANI 96H.

| Opcode | Operand | Description                                    |

|--------|---------|------------------------------------------------|

| ORA    | R<br>or | Logical OR register or memory with accumulator |

|        | M       |                                                |

oThe contents of the accumulator are logically ORed with the contents of the register or memory.

oThe result is placed in the accumulator.

oS, Z, P are modified to reflect the result.

oCY and AC are reset.

o**Example**: ORA B or ORA M.

| Opcode | Operand    | Description                           |

|--------|------------|---------------------------------------|

| ORI    | 8-bit data | Logical OR immediate with accumulator |

oThe contents of the accumulator are logically ORed with the 8-bit data.

oThe result is placed in the accumulator.

oS, Z, P are modified to reflect the result.

oCY and AC are reset.

o**Example**: ORI 46H.

| Opcode | Operand | Description                         |

|--------|---------|-------------------------------------|

| XRA    | R       | Logical XOR register or memory with |

|        | or      | accumulator                         |

|        | М       |                                     |

oThe contents of the accumulator are XORed with the contents of the register or memory.

oThe result is placed in the accumulator.

oS, Z, P are modified to reflect the result of the operation.

oCY and AC are reset.

oExample: XRA C or XRA M.

| Opcode | Operand    | Description                    |

|--------|------------|--------------------------------|

| XRI    | 8-bit data | XOR immediate with accumulator |

oThe contents of the accumulator are XORed with the 8bit data.

oThe result is placed in the accumulator.

oS, Z, P are modified to reflect the result.

oCY and AC are reset.

o**Example**: XRI 16H.

| Opcode | Operand | Description             |

|--------|---------|-------------------------|

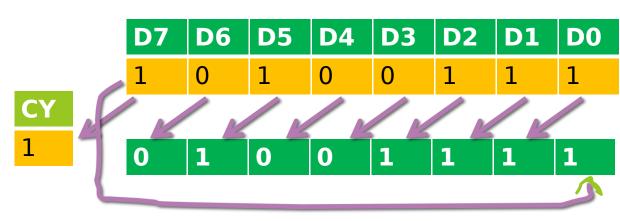

| RLC    | None    | Rotate accumulator left |

oEach binary bit of the accumulator is rotated left by one position.

oBit D7 is placed in the position of D0 as well as in the Carry f lag.

oCY is modified according to bit D7.

oExample: RLC.

| Opcode | Operand | Description              |

|--------|---------|--------------------------|

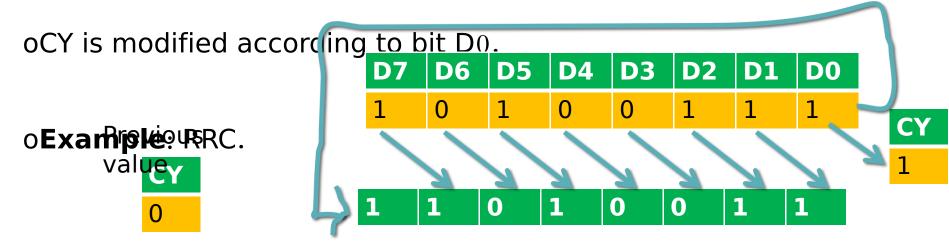

| RRC    | None    | Rotate accumulator right |

oEach binary bit of the accumulator is rotated right by one position.

oBit D0 is placed in the position of D7 as well as in the Carry f lag.

| Opcode | Operand                                    | Description |

|--------|--------------------------------------------|-------------|

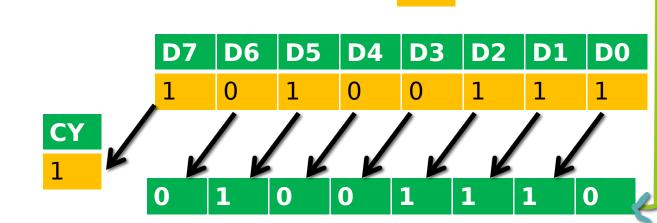

| RAL    | None Rotate accumulator left through carry |             |

|        |                                            |             |

oEach binary bit of the accumulator is rotated left by one position through the Carry flag.

oBit D7 is placed in the Carry flag, and the Carry f lag is placed in the least significant position  $D_0$ .

oCY is modified according to bit D7.

oExample: RAL.

CY

| Opcode | Operand | Description                            |

|--------|---------|----------------------------------------|

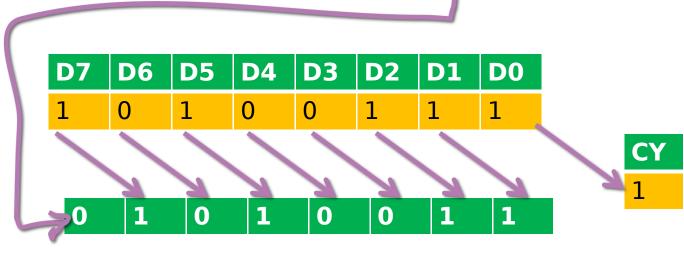

| RAR    | None    | Rotate accumulator right through carry |

oEach binary bit of the accumulator is rotated right by one position through the Carry f lag.

oBit D0 is placed in the Carry f lag, and the Carry f lag is placed in the most significant position D7.

oCY is modified according to bit D0.

o**Example**: RAR.

0

| Opcode | Operand | Description            |

|--------|---------|------------------------|

| СМА    | None    | Complement accumulator |

oThe contents of the accumulator are complemented.

oNo flags are affected.

oExample: CMA.

| Opcode | Operand | Description      |

|--------|---------|------------------|

| СМС    | None    | Complement carry |

oThe Carry f lag is complemented.

oNo other f lags are affected.

oExample: CMC.

| Opcode | Operand | Descriptio |  |

|--------|---------|------------|--|

|        |         | n          |  |

| STC    | None    | Set carry  |  |

• The Carry f lag is set to 1.

• No other flags are affected.

• Example: STC.

## **Branching Instructions**

| Opcode | Operand        | Description          |

|--------|----------------|----------------------|

| JMP    | 16-bit address | Jump unconditionally |

oThe program sequence is transferred to the memory location specified by the 16-bit address given in the operand.

oExample: JMP 2094 H.

## **Branching Instruction**

| Opcode | Operand        | Description        |

|--------|----------------|--------------------|

| Jx     | 16-bit address | Jump conditionally |

oThe program sequence is transferred to the memory location specified by the 16-bit address given in the operand based on the specified f lag of the PSW.

o**Example**: JZ 2094 H.

# Jump Conditionally

| Opcod | Description         | Status Flags |

|-------|---------------------|--------------|

| e     |                     |              |

| JC    | Jump if Carry       | CY =         |

|       |                     | 1            |

| JNC   | Jump if No Carry    | CY =         |

|       |                     | 0            |

| JP    | Jump if Positive    | S =          |

|       |                     | 0            |

| JM    | Jump if Minus       | S =          |

|       |                     | 1            |

| JZ    | Jump if Zero        | Z =          |

|       |                     | 1            |

| JNZ   | Jump if No Zero     | Z =          |

|       |                     | 0            |

| IDE   | lump if Parity Evon | D —          |

## **Branching Instruction**

| Opcode | Operand        | Descriptio           |  |

|--------|----------------|----------------------|--|

|        |                | n                    |  |

| CALL   | 16-bit address | Call unconditionally |  |

oThe program sequence is transferred to the memory location specified by the 16-bit address given in the operand.

oBefore the transfer, the address of the next instruction after CALL (the contents of the program counter) is pushed onto the stack.

oExample: CALL 2094 H.

## **Branching Instruction**

| Opcode | Operand        | Descrip            | otion |

|--------|----------------|--------------------|-------|

| Сх     | 16-bit address | Call conditionally |       |

o The program sequence is transferred to the memory location specified by the 16-bit address given in the operand based on the specified f lag of the PSW.

oBefore the transfer, the address of the next instruction after the call (the contents of the program counter) is pushed onto the stack.

o**Example**: CZ 2094 H.

## Call Conditionally

| Opcode | Description         | Status Flags |

|--------|---------------------|--------------|

| CC     | Call if Carry       | CY =         |

|        |                     | 1            |

| CNC    | Call if No Carry    | CY =         |

|        |                     | 0            |

| СР     | Call if Positive    | S =          |

|        |                     | 0            |

| СМ     | Call if Minus       | S =          |

|        |                     | 1            |

| CZ     | Call if Zero        | Z =          |

|        |                     | 1            |

| CNZ    | Call if No Zero     | Z =          |

|        |                     | 0            |

| CPE    | Call if Parity Even | P =          |

|        |                     | 1            |

| СРО    | Call if Parity Odd  | P =          |

## **Branching Instruction**

| Opcode | Operand | Description            |

|--------|---------|------------------------|

| RET    | None    | Return unconditionally |

oThe program sequence is transferred from the subroutine to the calling program.

oThe two bytes from the top of the stack are copied into the program counter, and program execution begins at the new address.

#### o**Example**: RET.

#### **Branching Instruction**

| Opcode | Operand | Description          |

|--------|---------|----------------------|

| Rx     | None    | Return conditionally |

oThe program sequence is transferred from the subroutine to the calling program based on the specified f lag of the PSW.

oThe two bytes from the top of the stack are copied into the program counter, and program execution begins at the new address.

oExample: RZ.

## **Return Conditionally**

| Opcode | Description           | Status Flags |

|--------|-----------------------|--------------|

| RC     | Return if Carry       | CY = 1       |

| RNC    | Return if No Carry    | CY = 0       |

| RP     | Return if Positive    | S = 0        |

| RM     | Return if Minus       | S = 1        |

| RZ     | Return if Zero        | Z = 1        |

| RNZ    | Return if No Zero     | Z = 0        |

| RPE    | Return if Parity Even | P = 1        |

| RPO    | Return if Parity Odd  | P = 0        |

## **Branching Instruction**

| Opcode | Operand | Descriptio                    |

|--------|---------|-------------------------------|

|        |         | n                             |

| RST    | 0 – 7   | Restart (Software Interrupts) |

oThe RST instruction jumps the control to one of eight memory locations depending upon the number.

oThese are used as software instructions in a program to transfer program execution to one of the eight locations.

oExample: RST 3.

## **Restart Address Table**

| Instructions | Restart Address |

|--------------|-----------------|

| RST 0        | 0000 H          |

| RST 1        | 0008 H          |

| RST 2        | 0010 H          |

| RST 3        | 0018 H          |

| RST 4        | 0020 H          |

| RST 5        | 0028 H          |

| RST 6        | 0030 H          |

| RST 7        | 0038 H          |

| Opcode | Operand | Descripti    |

|--------|---------|--------------|

|        |         | on           |

| NOP    | None    | No operation |

oNo operation is performed.

oThe instruction is fetched and decoded but no operation is executed.

oExample: NOP

| Opcode | Operand | Description |

|--------|---------|-------------|

| HLT    | None    | Halt        |

oThe CPU finishes executing the current instruction and halts any further execution.

oAn interrupt or reset is necessary to exit from the halt state.

oExample: HLT

| Opcode | Operand | Description       |

|--------|---------|-------------------|

| DI     | None    | Disable interrupt |

oThe interrupt enable f lip-f lop is reset and all the interrupts except the TRAP are disabled.

oNo f lags are affected.

oExample: DI

| Opcode | Operand | Descriptio       |

|--------|---------|------------------|

|        |         | n                |

| EI     | None    | Enable interrupt |

oThe interrupt enable f lip-f lop is set and all interrupts are enabled.

oNo flags are affected.

oThis instruction is necessary to re-enable the interrupts (except TRAP).

#### oExample: El

| Opcode | Operand | Descriptio          |

|--------|---------|---------------------|

|        |         | n                   |

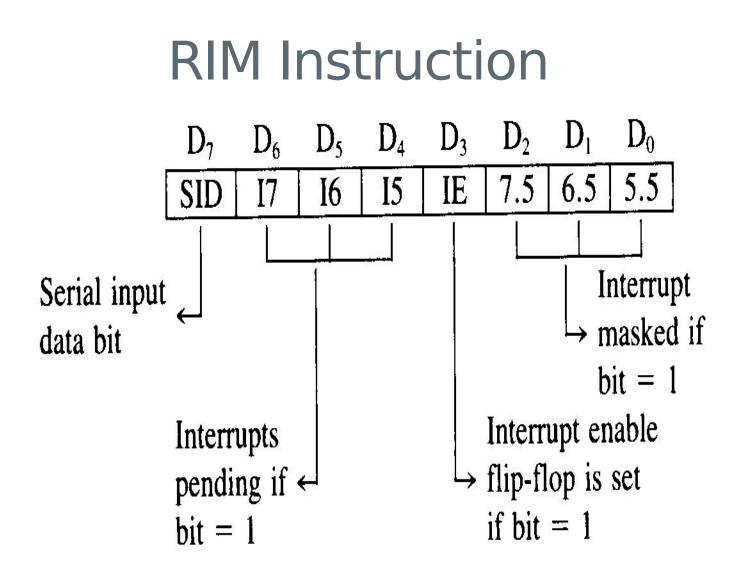

| RIM    | None    | Read Interrupt Mask |

oThis is a multipurpose instruction used to read the status of interrupts 7.5, 6.5, 5.5 and read serial data input bit.

oThe instruction loads eight bits in the accumulator with the following interpretations.

#### o**Example**: RIM

| Opcode | Operand | Description        |

|--------|---------|--------------------|

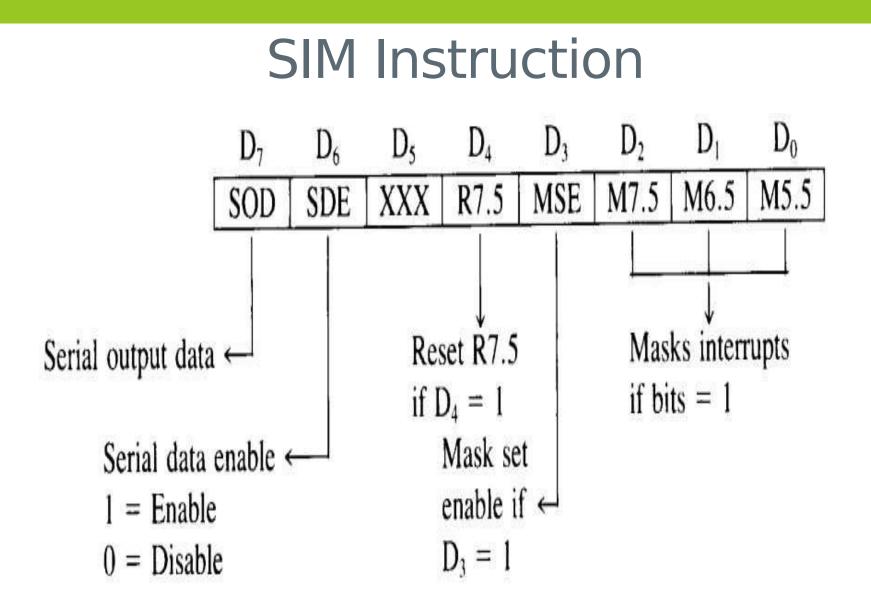

| SIM    | None    | Set Interrupt Mask |

oThis is a multipurpose instruction and used to implement the 8085 interrupts 7.5, 6.5, 5.5, and serial data output. oThe instruction interprets the accumulator

contents as follows.

oExample: SIM

# Addressing mode

- The 8085 has the following 5 different types of addressing Modes.

- 1. Immediate Addressing

- 2. Direct Addressing

- 3. Register Addressing

- 4. Register Indirect Addressing

- 5. Implied Addressing

## Immediate Addressing Mode

- In immediate addressing mode, the data is specified in the instruction itself. The data will be a part of the program instruction.

- Example

- MVI B, 37H Move the data 37H given in the instruction to B register;

- LXI D, 3100H.

- ADI 60H

# Direct Addressing Mode

- In direct addressing mode, the address of the data is specified in the instruction. The data will be in memory.

- Example

- LDA 2050H Load the data available in memory location 1050H in to accumulator

- STA 2055H

# Register Addressing Mode

- In register addressing mode, the instruction specifies the name of the register in which the data is available.

- Example

- MOV B, C Move the content of B register to A register

ADD B

# Register Indirect Addressing Mode

- In register indirect addressing mode, the instruction specifies the name of the register in which the address of the data is available. Here the data will be in memory and the address will be in the register pair.

- Example

- MOV A, M The memory data addressed by H L pair is moved to A register

- LDAX D

- STAX D

# Implied Addressing Mode

- In implied addressing mode, the instruction itself specifies the data to be operated.

- Example

- CMA Complement the content of accumulator,

- RAL Rotate accumulator left through carry.

# Identify the Addressing mode of following instructions

- ORA B

- MVI C,21H

- LHLD 2000H

- LDAX B

- LDA 2000H

- CMP B

- STC

- XCHG

- DAD

- DAA