### Digital System Design using HDL(EC0419) Unit-2 B.Tech (Electronics and Communication) Semester-IV

## Faculty Name : Prof. Miloni Ganatra

Academic Year 2020

# Unit 2: Gate Level Modeling

#### Gate Level Modeling:

Introduction, Gate level Primitive, Module Structure, Instances of Primitives, Gate Delays, <u>Designing Using Primitives</u>.

## Gate Level Modeling

- Steps

- Develope the boolean function of output

- Draw the circuit with logic gates/primitives

- Connect gates/primitives with net (usually wire)

- Figure HDL: Hardware Description Language

- Figure out architecture first, then write code.

### Gate Level

• At the next higher level of abstraction,

design is carried out in terms of basic gates.

• All the basic gates are available as ready modules called "*Primitives*".

## Primitives

- Primitives are modules ready to be instanced

- Smallest modeling block for simulator

- Verilog build-in primitive gate

- and, or, not, buf, xor, nand, nor, xnor

- prim\_name inst\_name( output, in0, in1,.... );

- User defined primitive (UDP)

- building block defined by designer

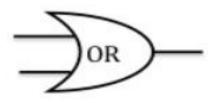

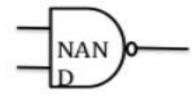

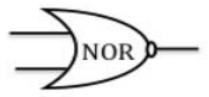

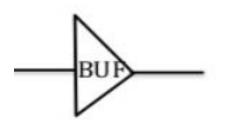

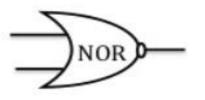

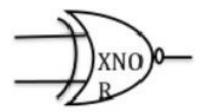

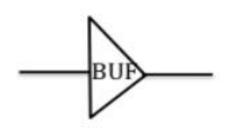

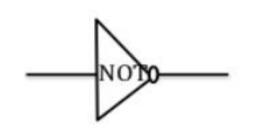

## Gate primitives

- Gate primitives are predefined in Verilog, which are ready to use.

- They are instantiated like modules. There are two classes of gate primitives:

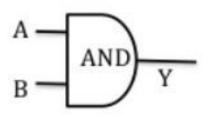

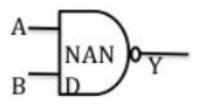

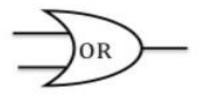

- Multiple input gate primitives and Single input gate primitives. Multiple input gate primitives include and, nand, or, nor, xor, and xnor. These can have multiple inputs and a single output.

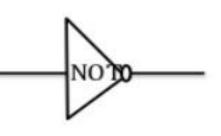

- □ Single input gate primitives include not, buf

# Gate level Abstraction

- This is also known as structural level Abstraction.

- In this level the Design is described in terms of gates.

- It is very easy to design any circuit in verilog if we have the structure.

- For large circuit its difficult to implement in gate level.

Instantiation of gates input wire a, b; output wire y; and a1 (y, a, b); nand n1 (y, a, b); or o1 (y, a, b); nor no1 (y, a, b); xor x1 ( y , a, b); xnor xn1 (y, a, b); buf b1 (out,in); not n1 (out,in);

## GATE LEVEL MODELING

• All the basic gates are available as "Primitives" in Verilog.

| Gate | Mode of instantiation             | Output port(s) | Input port(s) |

|------|-----------------------------------|----------------|---------------|

| AND  | and ga ( o, i1, i2, i8);          | 0              | i1, i2,       |

| OR   | or gr ( o, i1, i2, i8);           | 0              | i1, i2,       |

| NAND | nand gna ( o, i1, i2, i8);        | 0              | i1, i2,       |

| NOR  | nor gnr ( o, i1, i2, i8);         | 0              | i1, i2,       |

| XOR  | <b>xor</b> gxr ( o, i1, i2, i8);  | 0              | i1, i2,       |

| XNOR | <b>xnor</b> gxn ( o, i1, i2, i8); | 0              | i1, i2,       |

| BUF  | buf gb ( o1, o2, i);              | 01, 02, 03,    | i             |

| NOT  | not gn (o1, o2, o3, i);           | 01, 02, 03,    | i             |

| AND | 0 | 1 | х | Z |

|-----|---|---|---|---|

| 0   | 0 | 0 | 0 | 0 |

| 1   | 0 | 1 | Х | х |

| х   | 0 | Х | Х | х |

| Z   | 0 | х | х | х |

| NAND | 0 | 1 | X | Z | _ |

|------|---|---|---|---|---|

| 0    | 1 | 1 | 1 | 1 |   |

| 1    | 1 | 0 | Х | х |   |

| х    | 1 | х | Х | х |   |

| z    | 1 | х | Х | х |   |

| OR | 0 | 1 | X | Z |  |

|----|---|---|---|---|--|

| 0  | 0 | 1 | Х | х |  |

| 1  | 1 | 1 | 1 | 1 |  |

| Х  | х | 1 | х | х |  |

| Z  | х | 1 | х | х |  |

| NOR | 0 | 1 | х | Z |  |

|-----|---|---|---|---|--|

| 0   | 1 | 0 | Х | х |  |

| 1   | 0 | 0 | 0 | 0 |  |

| х   | х | 0 | х | х |  |

| Z   | х | 0 | х | х |  |

| XOR | 0 | 1 | X | Z |  |

|-----|---|---|---|---|--|

| 0   | 0 | 1 | Х | Х |  |

| 1   | 1 | 0 | Х | х |  |

| Х   | Х | Х | Х | Х |  |

| Z   | Х | Х | Х | х |  |

| XNO<br>R | 0 | 1 | X | Z | _ |

|----------|---|---|---|---|---|

| 0        | 1 | 0 | Х | Х |   |

| 1        | 0 | 1 | Х | х |   |

| Х        | х | Х | Х | Х |   |

Buf | in out

-

| 1 | out |

|---|-----|

| 0 | 1   |

| 1 | 0   |

| х | х   |

| Z | x   |

|   |     |

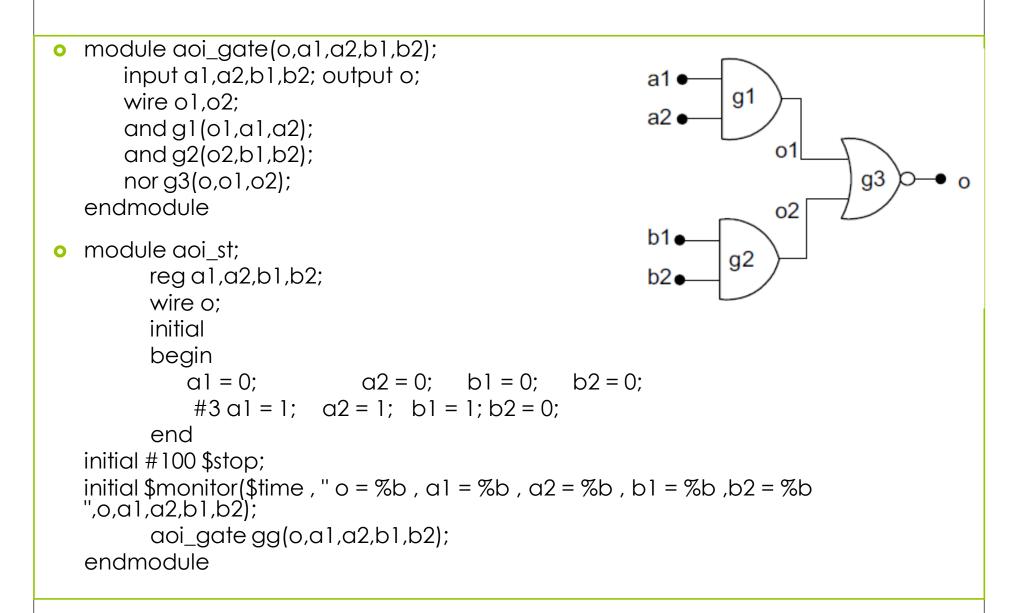

## Verilog module for AOI logic

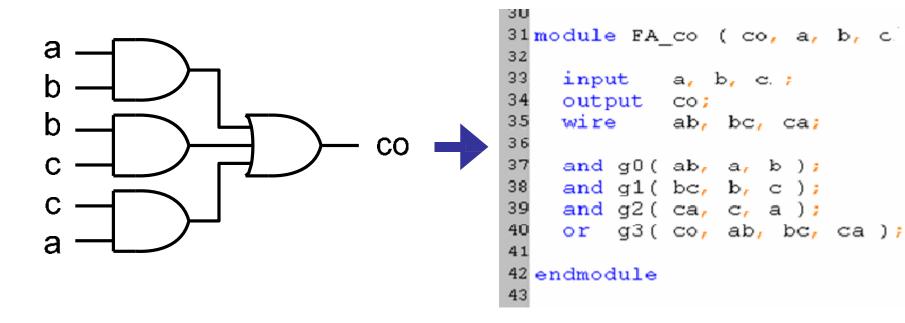

## $r co = (a \cdot b) + (b \cdot c) + (c \cdot a);$

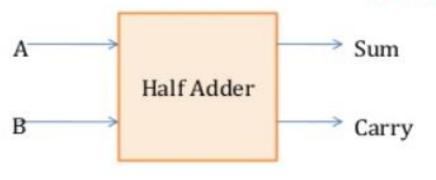

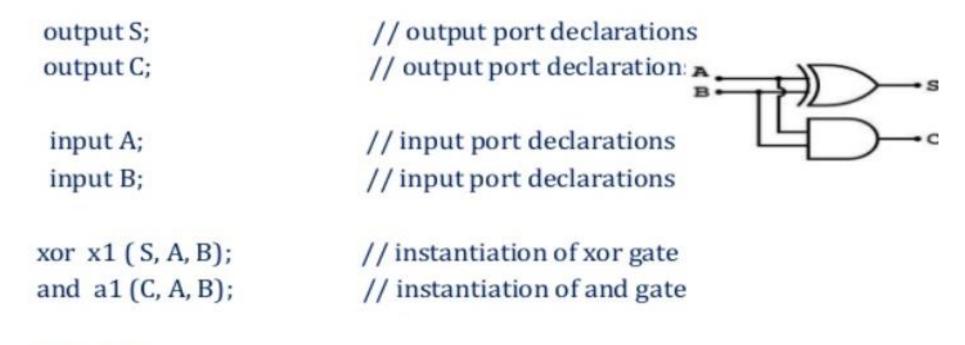

# Example of verilog Design using gate level

- I/P => A, B

- O/P => Sum & carry

| A | В | S | C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

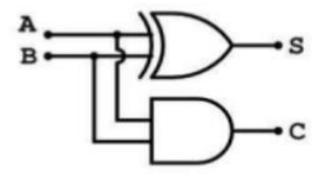

- Boolean Function

- Sum =  $A^B$

- Carry = A.B

# Example of verilog Design using gate level

// this is half adder verilog code

module half\_adder (S, C, A, B) // module name & port declaration

endmodule

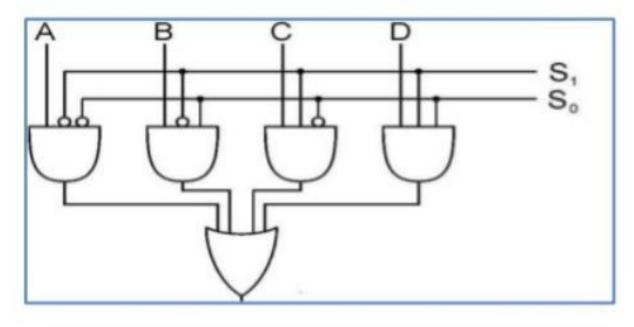

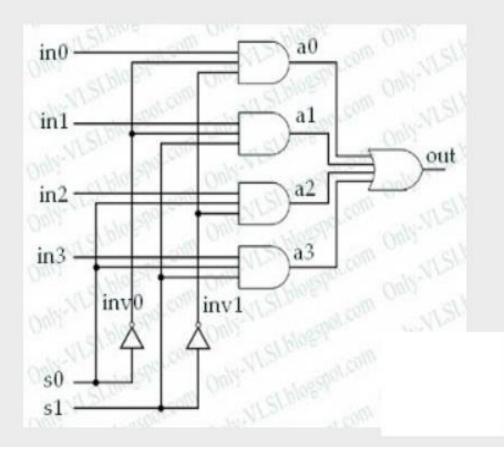

#### Gate level modeling of a 4x1 multiplexer.

The gate-level circuit diagram of 4x1 mux is shown below. It is used to write a module for 4x1 mux.

#### // port declarations

output out; // Output port.

input in0, in1, in2. in3; // Input ports.

input s0, s1; // Input ports: select lines.

# // intermediate wires wire inv0, inv1; // Inverter outputs. wire a0, a1, a2, a3; // AND gates outputs.

#### // Inverters.

not not\_0 (inv0, s0); not not\_1 (inv1, s1); // 3-input AND gates.

and and\_0 (a0, in0, inv0, inv1);

and and\_1 (a1, in1, inv0, s1);

and and\_2 (a2, in2, s0, inv1);

and and 3 (a3, in3, s0, s1);

// 4-input OR gate.

or or\_0 (out, a0, a1, a2, a3);

endmodule

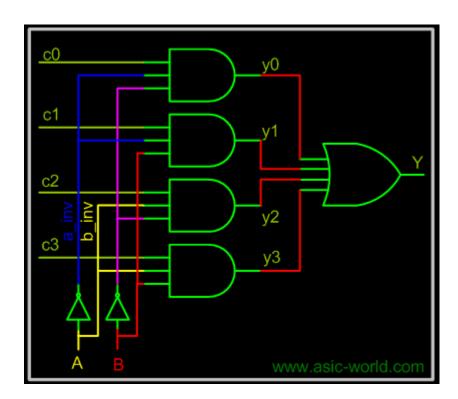

## Simulation of 4-1 Mux using Gate level

## // Testbench Code goes here initial begin

```

(

c0, c1, c2, c3, A, B, Y);

c0 = 0;

c1 = 0;

c2 = 0;

c3 = 0;

A = 0;

B = 0;

#1 A = 1;

#2 B = 1;

#4 A = 0;

#8 $finish;

end

```

## ARRAY OF INSTANCES OF PRIMITIVES

```

• and gate [7 : 4 ] (a, b, c);

```

```

and gate [7] (a[3], b[3], c[3]),

gate [6] (a[2], b[2], c[2]),

gate [5] (a[1], b[1], c[1]),

gate [4] (a[0], b[0], c[0]);

```

Syntax: and gate[mm : nn](a, b, c);

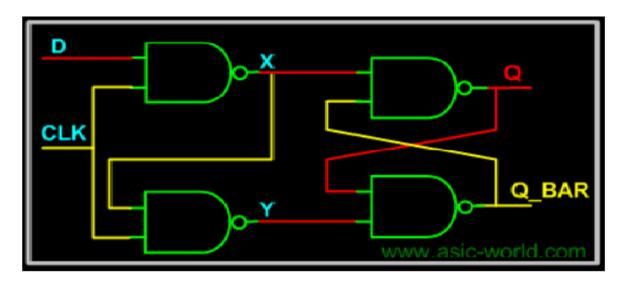

## D-Flip flop from NAND Gate (Gate Level)

#### D-Flip flop from NAND Gate

Verilog Code

```

1 module dff_from_nand();

2 wire Q,Q_BAR;

3 reg D,CLK;

4

5 nand U1 (X,D,CLK) ;

6 nand U2 (Y,X,CLK) ;

7 nand U3 (Q,Q_BAR,X);

8 nand U4 (Q_BAR,Q,Y);

9

```

## // Testbench of above code initial begin

| CLK | = 0; |    |

|-----|------|----|

| D = | 0;   |    |

| #3  | D =  | 1; |

| #3  | D =  | 0; |

|     |      |    |

end

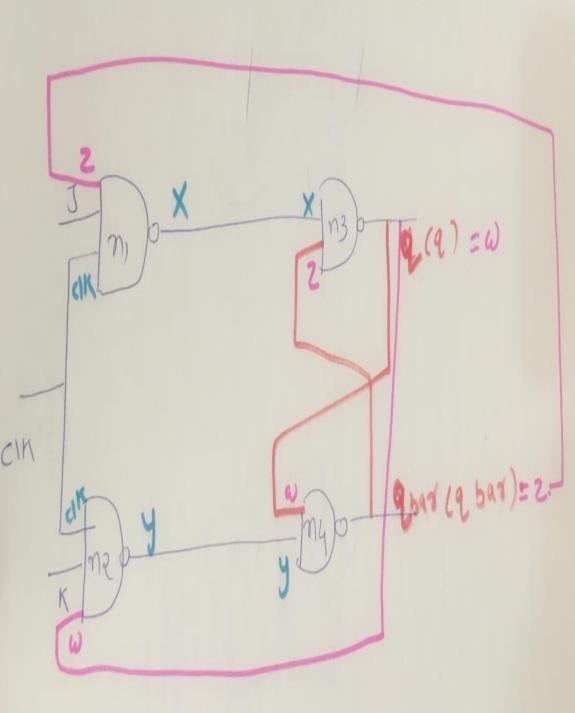

## JK flip flop using gate level

```

module jkstruct(j,k,clk,q,qbar);

```

```

input j,k,clk;

```

```

output reg q,qbar;

```

```

initial begin q=1'b1;qbar=1'b0; end

```

```

wire x,y,w,z;

```

```

assign w=q;

```

```

assign z=qbar;

```

```

nand n1(x,z,j,clk);

```

```

nand n2(y,k,w,clk);

```

```

nand n3(q,x,z);

```

```

nand n4(qbar,y,w);

```

endmodule

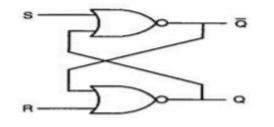

## SR latch using gate level

#### LOGIC DIAGRAM

#### VERILOG CODE

module srg(s,r,q,qb);

input s;

input r;

inout q;

inout qb;

nor n1(qb,s,q);

nor n2(q,r,qb);

endmodule

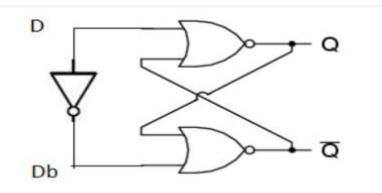

## D latch using gate level

module dlatch(d,db,q,qb); input d; input db; inout q; inout qb; not (db,d); nor n1(q,d,qb); nor n2(qb,db,q); endmodule

## Assignment

- Write a Verilog code for following digital circuit using gate level modeling.

- RS flip flop

- JK latch

- 3-8 Decoder

- 4-2 Encoder

- 8-1 Multiplexer

- 1-4 Demultiplexer